Lehrstuhl für Informatik 1 Friedrich-Alexander-Universität Erlangen-Nürnberg

# **BACHELOR THESIS**

# Advanced Vector Extensions to Accelerate Crypto Primitives

Johannes Götzfried

Erlangen, July 31, 2012

Examiner:Prof. Dr. Felix FreilingAdvisor:Tilo Müller

## Eidesstattliche Erklärung / Statutory Declaration

Hiermit versichere ich eidesstattlich, dass die vorliegende Arbeit von mir selbsttändig, ohne Hilfe Dritter und ausschließlich unter Verwendung der angegebenen Quellen angefertigt wurde. Alle Stellen, die wörtlich oder sinngemäß aus den Quellen entnommen sind, habe ich als solche kenntlich gemacht. Die Arbeit wurde bisher in gleicher oder ähnlicher Form keiner anderen Prüfungsbehörde vorgelegt.

I hereby declare formally that I have developed and written the enclosed thesis entirely by myself and have not used sources or means without declaration in the text. Any thoughts or quotations which were inferred from the sources are marked as such. This thesis was not submitted in the same or a substantially similar version to any other authority to achieve an academic grading.

Erlangen, July 31, 2012

Johannes Götzfried

#### Zusammenfassung

Verschlüsselung spielt eine große Rolle in der heutigen IT-Sicherheit und wird in der Regel täglich von jedem benutzt, der mit elektronischen Geräten arbeitet. Obwohl die Rechenleistung stetig wächst, bleibt die Effizienz von kryptographischen Algorithmen ein wichtiges Thema. In dieser Arbeit werden daher schnelle Implementierungen der fünf symmetrischen Blockchiffren Serpent, Twofish, Blowfish, Cast-128 und Cast-256 vorgestellt. Die Implementierungen benutzen die *Advanced Vector Extensions* (AVX), ein neues SIMD Instruktionsset, und den Nachfolger AVX2, der von zukünftigen Prozessoren unterstützt wird. Des Weiteren wurde die AVX Implementierung von jedem Algorithmus in den Linux Kernel integriert und überbietet die derzeitig schnellste Implementierung in jedem der fünf Fälle.

#### Abstract

Encryption plays an important role in today's IT-Security and is generally used by everybody who is working with electronic devices on a daily basis. Although computing power increases steadily, the performance of cryptographic algorithms remains an important topic. In this thesis fast implementations of the five symmetric block ciphers Serpent, Twofish, Blowfish, Cast-128 and Cast-256 are presented. The implementations make use of the *Advanced Vector Extensions* (AVX), a newly introduced SIMD instruction set, and its successor AVX2, which will be supported by future CPUs. Furthermore the AVX implementation of each algorithm has been integrated into the Linux kernel and outperforms the currently fastest implementation in each of the five cases.

# CONTENTS

| 1 | Intro | oductio                     | on                    | 1    |  |  |  |  |  |

|---|-------|-----------------------------|-----------------------|------|--|--|--|--|--|

|   | 1.1   | Motiva                      | ation                 | . 2  |  |  |  |  |  |

|   | 1.2   | Task .                      |                       | . 2  |  |  |  |  |  |

|   | 1.3   | Related Work                |                       |      |  |  |  |  |  |

|   | 1.4   | Results                     |                       |      |  |  |  |  |  |

|   | 1.5   | Outline                     | e                     | . 4  |  |  |  |  |  |

|   | 1.6   | Acknow                      | wledgments            | . 4  |  |  |  |  |  |

| _ | _     | _                           |                       |      |  |  |  |  |  |

| 2 |       | ackground                   |                       |      |  |  |  |  |  |

|   | 2.1   | •                           | etric Ciphers         |      |  |  |  |  |  |

|   |       | 2.1.1                       | Modes of Operation    |      |  |  |  |  |  |

|   |       | 2.1.2                       | AES Competition       |      |  |  |  |  |  |

|   |       | 2.1.3                       | Serpent               | . 8  |  |  |  |  |  |

|   |       | 2.1.4                       | Twofish               | . 11 |  |  |  |  |  |

|   |       | 2.1.5                       | Blowfish              | . 14 |  |  |  |  |  |

|   |       | 2.1.6                       | Cast-128              | . 15 |  |  |  |  |  |

|   |       | 2.1.7                       | Cast-256              | . 16 |  |  |  |  |  |

|   | 2.2   | Advan                       | ced Vector Extensions | . 16 |  |  |  |  |  |

|   |       | 2.2.1                       | Registers             | . 17 |  |  |  |  |  |

|   |       | 2.2.2                       | Instruction Set       | . 18 |  |  |  |  |  |

|   |       | 2.2.3                       | AVX2                  | . 22 |  |  |  |  |  |

|   | 2.3   | The Linux Kernel         25 |                       |      |  |  |  |  |  |

|   |       | 2.3.1                       | Kernel Development    | . 25 |  |  |  |  |  |

|   |       | 2.3.2                       | Source Tree           | . 26 |  |  |  |  |  |

|   |       | 2.3.3                       | Cryptographic API     | . 27 |  |  |  |  |  |

| 3 | Imn   | lement                      | ation                 | 29   |  |  |  |  |  |

| 3 | 3.1   |                             |                       |      |  |  |  |  |  |

|   | 5.1   | Serpen                      |                       |      |  |  |  |  |  |

|   |       | 3.1.1                       | AVX Implementation    |      |  |  |  |  |  |

|   |       | 3.1.2                       | AVX2 Implementation   |      |  |  |  |  |  |

|   |       | 3.1.3                       | Kernel Integration    |      |  |  |  |  |  |

|   | 3.2   |                             | h                     |      |  |  |  |  |  |

|   |       | 3.2.1                       | AVX Implementation    |      |  |  |  |  |  |

|   |       | 3.2.2                       | AVX2 Implementation   |      |  |  |  |  |  |

|   |       | 3.2.3                       | Kernel Integration    | . 40 |  |  |  |  |  |

| 3.3 Blowfish                 |                   |                 | sh                  | . 41 |  |  |  |

|------------------------------|-------------------|-----------------|---------------------|------|--|--|--|

|                              |                   | 3.3.1           | AVX Implementation  | . 41 |  |  |  |

|                              |                   | 3.3.2           | AVX2 Implementation | . 43 |  |  |  |

|                              |                   | 3.3.3           | Kernel Integration  | . 43 |  |  |  |

|                              | 3.4               | 28              | . 44                |      |  |  |  |

|                              |                   | 3.4.1           | AVX Implementation  | . 44 |  |  |  |

|                              |                   | 3.4.2           | AVX2 Implementation | . 46 |  |  |  |

|                              |                   | 3.4.3           | Kernel Integration  | . 46 |  |  |  |

|                              | 3.5               | .5 Cast-256     |                     |      |  |  |  |

|                              |                   | 3.5.1           | AVX Implementation  | . 47 |  |  |  |

|                              |                   | 3.5.2           | AVX2 Implementation | . 48 |  |  |  |

|                              |                   | 3.5.3           | Kernel Integration  | . 48 |  |  |  |

| 4 Evaluation                 |                   |                 |                     |      |  |  |  |

|                              | 4.1               | Code Statistics | . 52                |      |  |  |  |

|                              | 4.2 Compatibility |                 | tibility            | . 54 |  |  |  |

|                              | 4.3 Correctness   |                 |                     | . 55 |  |  |  |

|                              | 4.4               | 4.4 Performance |                     |      |  |  |  |

|                              |                   | 4.4.1           | Serpent             | . 58 |  |  |  |

|                              |                   | 4.4.2           | Twofish             | . 59 |  |  |  |

|                              |                   | 4.4.3           | Blowfish            | . 61 |  |  |  |

|                              |                   | 4.4.4           | Cast-128            | . 62 |  |  |  |

|                              |                   | 4.4.5           | Cast-256            | . 63 |  |  |  |

|                              | 4.5               | Security        | y                   | . 64 |  |  |  |

| 5 Conclusion and Future Work |                   |                 |                     | 67   |  |  |  |

|                              | 5.1               | Limitat         | ions                | . 67 |  |  |  |

|                              | 5.2               | Future '        | Work                | . 68 |  |  |  |

|                              | 5.3               | Conclus         | sion                | . 69 |  |  |  |

| Bibliography 71              |                   |                 |                     |      |  |  |  |

1

# INTRODUCTION

Disk encryption is now widely spread and there are numerous software solutions available, which protect your private data or even your whole hard disk. Most popular services on the Internet, e.g. SMTP, HTTP and SSH, work at least optionally with encryption as additional layer to provide transport security. Hashing is often used to verify a message's integrity and in combination with asymmetric ciphers signatures can be implemented. Software distributors are able to sign their packages with a master-key to verify that they have not been modified and the services mentioned above are able to use signatures to prevent man-in-the-middle attacks.

Despite all the advantages of these techniques, however, there are drawbacks. The performance of a system, that uses cryptography, cannot be as good as the performance of a system, that does not use it. But there are many cases, where the use of encryption techniques is mandatory. More and more people carry sensitive and confidential data about. Employees, that work outside their office or need to travel a lot, are often forced by company regulations to use disk encryption for their mobile devices. A remote connection for controlling machines needs to be secure against eavesdropping and man-in-the-middle attacks as well as a connection used for online banking. In that cases lower performance has to be accepted, but by speeding up cryptographic algorithms the decrease can be minimized.

Because of these and other use cases, the performance of cryptographic algorithms is a big issue. Lowlevel implementations of crypto primitives, that exploit platform specific assembler implementations, can achieve a considerable gain in performance as compared to generic C implementations. For this thesis, five common symmetric block ciphers, Serpent, Twofish, Blowfish, Cast-128 and Cast-256, have been implemented, exploiting the new *Advanced Vector Extensions* (AVX) and its successor AVX2. As softwarebased solutions, the AVX implementations are running on recent CPUs, which support AVX. The AVX2 implementations will run on upcoming Intel CPUs launching market not before 2013. Additionally a patch for the Linux kernel has been developed for each AVX implementation. This makes it possible to use the AVX implementations on any standard Linux system in combination with the device mapper dm-crypt for disk encryption or any other application relying on the kernel crypto API.

## 1.1 Motivation

Some time ago processor manufactures introduced SIMD instruction sets, which allow to process multiple data with only one instruction. Many of the scalar instructions have SIMD equivalents and can be used to operate on more values in parallel. In practice SIMD instructions operate on large registers, that are for example 128 bit wide. They have the ability to fill registers from memory and to modify parts of them in a similar manner. There have been some of these SIMD instruction sets in history, namely MMX, SSE, SSE2, SSSE3, and Intel has released a new instruction set called AVX (Advanced Vector Extensions) [36] in 2011. AVX has some interesting new features. The 128 bit registers have been expanded to 256 bits, a nondestructive three-operand syntax has been added and a new extension coding scheme (VEX) has been designed. With this new features AVX is a good choice for accelerating crypto primitives.

At the beginning of this thesis, it has also been considered to speed up hash algorithms. Currently there is a competition [50] running to select a new SHA-3 function and to replace SHA-1 and SHA-2. Since theoretical attacks on SHA-1 have been carried out and SHA-1 and SHA-2 are algorithmically similar it has been decided to start a competition for a new hash standard. In this competition there are five finalists BLAKE [6], Grøstl [16], JH [59], Keccak [8] and Skein [15]. One big selection factor for the winner of this competition is, besides security, performance and that is why there were plans to accelerate one of the five SHA-3 finalists with AVX.

It has turned out, however, that symmetric ciphers can get a better performance boost, because in most modes of operation, it is possible to process many blocks in parallel, whereas with hash algorithms the blocks would have to be processed sequentially. Moreover the integration into the Linux kernel would probably not have been possible in the way, we did it with the symmetric ciphers, because the finalist has not been selected yet.

As stated above there is a demand for fast implementations of symmetric block ciphers. With AESNI [31] Intel introduced an instruction set, which implements AES [43], the most popular and widely spread block cipher, in hardware. This step made a very fast implementation of AES available to everybody, who uses x86 hardware. Other symmetric block ciphers, however, which are widely used, too, cannot benefit from the AESNI instruction set and therefore they have to be accelerated with a different approach. The current situation leads to the motivation to reimplement popular block ciphers with AVX. The ciphers related to AES, for example Serpent [4] and Twofish [53], are of special interest, because they were among the five finalists in the AES competition and have practical relevance.

As disk encryption is a very popular and the most performance critical use case of symmetric ciphers, it is a good choice to test our implementations in that field. There are different software solutions available and among these the Linux kernel itself provides support for all kinds of disk encryption. As Linux is an open source operating system, we are able to integrate our ciphers into the kernel and make meaningful speed tests in kernel space. Furthermore, integrating our ciphers into the Linux kernel makes the implementations available to many people at once and helps reproducing the results of this thesis.

# 1.2 Task

The goal of this thesis is to improve the performance of symmetric block ciphers using AVX. For each algorithm, Serpent [4], Twofish [53], Blowfish [52], Cast-128 [1] and Cast-256 [2], a plain assembler implementation has to be developed. All implementations are based on the concept of parallel processing sequenced blocks. The challenge is to transform the specification or the reference implementation to an implementation that makes use of the SIMD instructions and exploits the resulting parallelism. But there are operations, which cannot be transformed to equivalent SIMD operations, and in this case we have to work around the problem and make it possible to exploit AVX anyway.

AVX lacks some instructions, basically table lookups, which would be necessary to fully parallelize all implementations. Furthermore the 256 bit wide registers cannot be used efficiently with integer instructions, but instead these operations can just be applied on 128 bit wide registers. Both facts are serious drawbacks

and therefore every algorithm has also been implemented with the successor AVX2, which does not have these restrictions. For AVX2, however, there currently exists no hardware, which could be used to test the implementations, and therefore the AVX2 implementations have to be tested within an emulator [10]. Of course it is not possible to measure the exact time our implementations will take on future CPUs, but based on the instructions used, it can be guessed how fast they will be, once the hardware is available.

The integration of an AVX implementation into the Linux kernel requires some extra work. The symmetric ciphers do not need to be adjusted, but a lot of gluecode has to be written to make the integration possible. The gluecode needs to register the cipher within the crypto API of the kernel and reimplement the modes of operation, which are provided by the kernel, because the ciphers process many blocks at once and therefore cannot make use of the standard implementation of the modes of operation. It is necessary to provide new and large testvectors for the specific ciphers in all available modes to allow the kernel doing a self-test. The implementations are integrated in such a way, that they can be loaded as separate kernel module. For the Cast-128 and Cast-256 integration even the generic implementations have to be adjusted, because at the time of this writing there has no accelerated implementation been present.

Besides all this details, the goal of this thesis is simple to summarize. It should be possible to get a significant performance boost for popular symmetric ciphers, exploiting AVX and AVX2.

### 1.3 Related Work

There are many attempts to accelerate crypto primitives. Usually a reference implementation is shipped along with the specification of a cryptographic algorithm and the authors already give hints, which parts are able to be parallelized or optimized. Often the authors themselves provide an accelerated version of the algorithm and for most ciphers at least an assembler implementation, that does not make use of SIMD instructions, exists. Many implementations, which exploit previous instruction sets, exist as there is demand for fast ciphers.

Regarding AVX, there are already implementations of crypto primitives, that exploit the new instruction set. Among the SHA-3 candidates Blake has already been implemented with AVX and AVX2 [47] and for Grøstl there also exist implementations, that make use of AVX and AVX2 [38].

During the work on this thesis and while submitting the patches with the AVX implementations to the Linux kernel, it has been discovered that one kernel developer, Jussi Kivilinna, works on AVX2 implementations of symmetric ciphers and their integration into the kernel, too [35]. He implemented Serpent, Twofish and Blowfish in a way, which is similar to the one in this thesis, but there are differences as well. He did not provide AVX implementations, however, and at the moment no other AVX implementations of the five ciphers, which were implemented during this thesis have been found.

Nevertheless these examples prove, that providing fast implementations of cryptographic algorithms is currently a hot topic in practical IT-Security.

## 1.4 Results

For five different algorithms fast implementations are provided with this thesis and for every algorithm an AVX implementation, an AVX2 implementation and a Linux kernel patch has been developed. Every of the five AVX implementations is faster than the previously fastest implementation in the Linux kernel has been. The AVX2 implementations have been evaluated based on the instruction counts and are expected to be a lot faster than the AVX implementations, but no timing results can be provided for them before AVX2 CPUs will be available in 2013. With the five ciphers Serpent, Twofish, Blowfish, Cast-128 and Cast-256 we have accelerated today's most important symmetric block ciphers, aside from AES, for which with AESNI already a fast implementation in hardware is available.

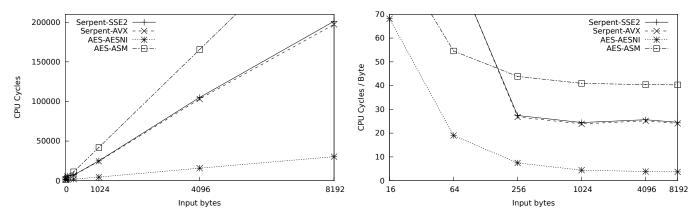

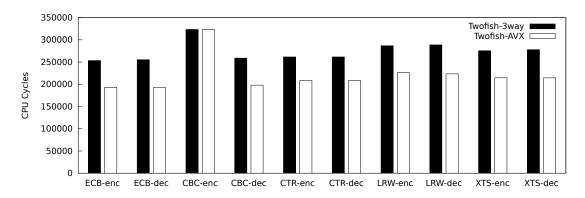

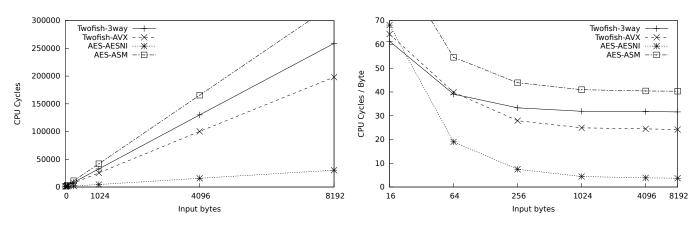

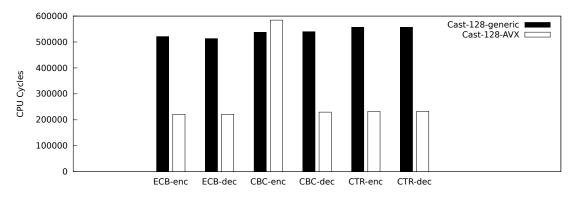

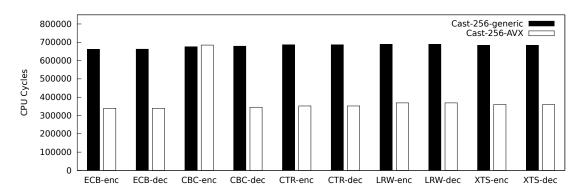

Our Serpent implementation is 6.1% faster than the current SSE2 implementation and Twofish has been accelerated by 30.8% compared to the previous 3-way parallel assembler implementation. Cast-128 is

about 115.8% faster and for Cast-256 we get a speedup of 88.6%. Finally for Blowfish we get a speedup of 0.8%, which is slightly better, but too low, to submit the cipher to the Linux kernel. These timings could be reproduced in userspace, kernelspace and while measuring the data rate in disk encryption tests.

In total ten different assembler implementations have been developed, five AVX implementations and five AVX2 implementations, and ten kernel patches have been submitted. All patches have been accepted and four patches, one patch for Serpent and three patches for Twofish, have already been merged into mainline. The other six patches, three for Cast-128 and another three for Cast-256, are about to be merged. Our implementation of Serpent and Twofish will be available with the official kernel version 3.6.

## 1.5 Outline

In chapter 2 the background information is given, which is necessary to understand the work, which has been done in this thesis. In section 2.1 an overview of symmetric ciphers is given, the modes of operation are explained and the candidates from the AES competition will be introduced. After this the five ciphers Serpent, Twofish, Blowfish, Cast-128 and Cast-256 are explained in detail, because they will be implemented later on. The AVX instruction set is shown in section 2.2 together with the successor AVX2. Finally in section 2.3 some explanations about the Linux kernel and particularly about kernel development and the crypto API are given.

Chapter 3 explains in detail, how the five ciphers have been implemented and integrated into the kernel. For every cipher the AVX implementation will be shown first and after that the differences that lead to the AVX2 implementation are described. Last but not least the kernel integration will be shown for every of the five ciphers.

In chapter 4 we make some tests with our implementations and see them from a different angle. In section 4.1 we show the source code statistics of the different kernel patches to give an overview on what has been changed by what patch. After that we want to show possibilities how the implementations can be used (section 4.2) and make plausible why our implementations are correct (section 4.3). The most important part is section 4.4, which contains a detailed performance evaluation of every implementation. Finally there are some considerations about the security of our implementations in section 4.5.

# 1.6 Acknowledgments

I want to thank my advisor Tilo Müller for giving me the chance, to work on this interesting topic, and supporting me. Furthermore I want to thank the Chair for IT Security Infrastructures for lending me a computer with an Intel Core i5-2500 CPU, which supports the new AVX instruction set natively and was used heavily during this thesis.

Last but not least, I want to thank my family, first and foremost my parents, for their personally encouragement and incessant support of my entire studies.

2

# BACKGROUND

This chapter provides you with the background information, which is useful or necessary to understand the implementation part of this thesis. First in section 2.1 an introduction about symmetric ciphers is given and the difference between symmetric and asymmetric ciphers will be explained. It would be beneficial to have some knowledge about this topic in advance, but the explanations given should be sufficient to understand most parts of this work. In this section the modes of operation (section 2.1.1) will be covered, which are needed to use ciphers on messages with arbitrary length. After that in section 2.1.2 the AES competition will be presented, where five different block ciphers have been chosen as finalists, which share some common properties. In section 2.1.3 and 2.1.4 two out of the five finalists will be introduced and explained in detail, because we will provide fast implementations for them. After that we will introduce three more symmetric ciphers, which were not among the five finalists, but are related to them. For every of the five presented ciphers we will provide a fast implementation and a kernel patch later on.

In section 2.2 the Advanced Vector Extensions are introduced. This is the extension, which we will use to implement our algorithms. It is no harm to have some background information about SIMD instruction sets, like MMX or SSE, in advance, but it is not necessary to understand the explanations given here. Nevertheless this section is not a guide to assembler programming in general and so you should at least be familiar with generic x86\_64 assembly and have some knowledge about the general purpose registers. In section 2.2.1 the new registers are presented and in section 2.2.2 a for this thesis relevant subset of the available instructions will be shown. Section 2.2.3 gives an overview of AVX2, the successor of AVX, which is not yet available on real hardware, but can already be used to develop applications and has some huge advantages over AVX.

We want to commit our ciphers to the Linux kernel, and that is why in section 2.3 some short informations about the kernel will be provided. In section 2.3.1 the development process of the kernel is explained. There are some useful informations you should know, if you want to contribute to the kernel. Section 2.3.2 shows the source tree of the Linux kernel and points out the positions where we have to place our implementations. Finally in section 2.3.3 a high level description of the Linux crypto API is provided. This API is used for all kind of cryptographic algorithms. Besides this API we will not need much internal kernel functionality and so it is not necessary to be an expert in kernel development to understand the patches we provide with our ciphers.

### 2.1 Symmetric Ciphers

Symmetric ciphers use the same key for the encryption of a plaintext message and the decryption of the corresponding ciphertext. There also exist asymmetric ciphers, which in contrast to symmetric ciphers, provide a public and a private key, so that the message can be encrypted using the public key and decrypted with the private key. This has the advantage, that no secret key has to be shared between the two parties, which want to exchange secret messages. One big drawback of symmetric cryptography is that both parties have to know a common secret key and therefore need to exchange this key over a somehow secured connection that nobody is able to eavesdrop. Asymmetric cryptography, however, is build on specific algebraic properties and therefore much slower than symmetric cryptography. This one reason, why symmetric cryptography is still very important and in many cases a hybrid approach is chosen. It is common, to use asymmetric cryptography with the shared secret key to exchange the actual information. As symmetric ciphers are used to encrypt the actual information, it is important, that they are very fast. Only symmetric cryptography is covered in this section. Asymmetric cryptography works completely different and to gain a performance boost would require a totally different approach.

When speaking of symmetric cryptography there exist in fact two types of algorithms: stream ciphers and block ciphers. Stream ciphers can take a message of arbitrary length and encrypt it on the fly, i.e. digit by digit, whereat a digit is typically a bit. This can be achieved by generating some pseudo random keystream from an initially random seed and somehow operate with this keystream on the message. Usually just an exclusive-or is used to combine the keystream with the original message. Block ciphers, in contrast, take exactly one block, i.e. a fixed length of bits specified by the cipher (typically 64 or 128 bit), as input and usually output an encrypted block with exactly the same size. Many modern block ciphers work essentially similar. They need to be initialized with a key of fixed length (typically between 64 and 512 bit) and do some key scheduling to generate round keys out of the supplied fixed length key. In the encryption or decryption routine they process the data in a cipher and key size specific number of similar designed rounds. Often the rounds only differ in the round key used from the key schedule. Common operations in these rounds are substitutions, permutations and key mixing operations. Depending on these operations the block ciphers are classified in different categories, for example as substitution-permutation-network or Feistel network. The details are discussed in the specific sections, for example in section 2.1.3 and 2.1.4, where the two algorithms Serpent and Twofish are introduced. To be able to encrypt messages of arbitrary length with block ciphers, two additional mechanisms are needed. First of all the message might have to be padded, to get a length, which is a multiple of the block size. Now there are different modes of operation, which specify how the block cipher should be used to encrypt the whole message, because the cipher itself is only able to encrypt exactly one block. The different possibilities will be shown in the next section.

#### 2.1.1 Modes of Operation

The modes of operation, which should be used in conjunction with symmetric block ciphers, are published by the National Institute of Standards and Technology (NIST). The first modes of operation were published in 1980 to be used with the former Data Encryption Standard (DES) and are specified in FIPS 81 [41]. FIPS 81 already lists ECB and CBC, which is still in use today. In 2001, NIST renewed the specification, added the CTR mode and propagated the Advanced Encryption Standard (AES) as the default block cipher for these modes [44]. Nine years later in 2010, NIST added the XTS mode, which is used by disk encryption systems [45]. There exist more modes than the ones published by NIST, but this are the most important ones. When we want to speed up block ciphers by processing blocks in parallel, we have to know the different modes, as we have to reimplement them, to give them the ability to deal with our parallel implementation. We also have to check, whether the mode of operation actually supports parallel processing or not. In this section we want to take a closer look on three of the modes: ECB, CBC and CTR. This are three of the modes, available in the Linux kernel, and it should be possible to use them in conjunction with every block cipher.

The simplest of the modes is the *electronic codebook* (ECB) mode. For this mode the message has to have a length, which is a multiple of the block size of the underlaying block cipher. If this is not the case,

#### CHAPTER 2. BACKGROUND

padding is required. There exist several padding schemes and one common method is to add a single one bit followed by as much zero bits, as are necessary to fill the block. This has the advantage that the actual length of the message can be reconstructed, whereas this would not be possible by just adding zeros. The disadvantages are, that a whole block has to be added, if the message ends on a block boundary and that the lengths of the plaintext and the ciphertext are different. Of course no padding is required, if you can be sure, that the input data always has the right length. With ECB the message is just divided into blocks and each block is encrypted separately with the same key. Security is only provided on a per block basis, but the overall structure may be recovered, as identical plaintext blocks lead to identical ciphertext blocks. Decryption works similarly to the encryption and as the blocks are processed separately, parallelization is perfectly possible. Nevertheless, due to security issues, this mode should no longer be used in any field of application.

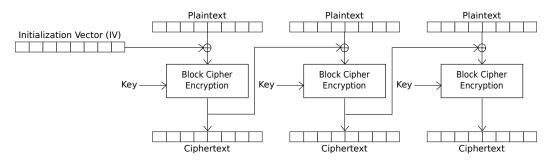

Another mode is *cipher block chaining* (CBC), which is very old, but still widely used and considered secure. It is the default mode used by most of the disk encryption systems. CBC essentially requires padding as well, however there exist more sophisticated padding schemes. The disadvantage of getting a different ciphertext length than the actual plaintext length can be resolved with a method called *ciphertext stealing* [46]. With ciphertext stealing some data of the next to last block is used for padding and thus encrypted twice. In contrast to ECB, with CBC the blocks are not encrypted separately, but instead each plaintext block is exclusive-or'ed with the previous ciphertext block before being encrypted. The first plaintext block is xor'ed with an *initialization vector* (IV). Figure 2.1 visualizes the encryption process. Because of chaining the blocks this way, every block is dependent upon its previous blocks and with the rhaining is, that we are forced to process the blocks sequentially. Decryption, however, can be parallelized, because each block is exclusive-or'ed with the previous chiphertext block *after* being decrypted. This means decryption and the following xor operation can be done in parallel.

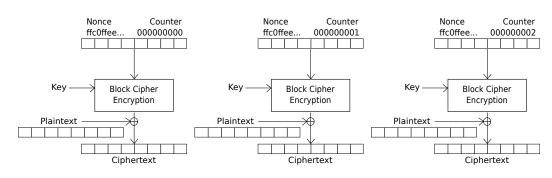

Figure 2.1: Cipher block chaining (CBC) mode encryption

The last mode presented here is *counter* (CTR). CTR does not require the message to be padded and is special, because it is able to turn the underlaying block cipher into a stream cipher. Therefore the keystream, or to be more precise, the next block of the keystream, is generated by encrypting successive values of a counter. The counter is independent from the actual plaintext message and may be a function producing a sequence. Of course CTR becomes more secure, if the sequence does not repeat, because otherwise the same problem as with ECB occurs. Most of the time, this function is just an increment-by-one, the Linux kernel uses this simple function as well, and some nonce may be added, which serves the same purpose as the initialization vector with CBC. After that, the keystream is simply xor'ed with the plaintext message. This can be done blockwise or digit by digit like an ordinary stream cipher would do it. Figure 2.2 shows an illustration of the encryption process. The decryption as well, to generate the identical keystream the same way. After that, the keystream is xor'ed with the ciphertext to reconstruct the original plaintext. As you can see in figure 2.2, there is no chaining between the different blocks and so both, encryption and decryption, can be easily parallelized. It might look strange, that the block cipher itself does not process the actual message, but just some counter values, however despite that, CTR is considered to be secure.

Figure 2.2: Counter (CTR) mode encryption

#### 2.1.2 AES Competition

At this point you should have a rough overview on what a block cipher is and you also have seen how these block ciphers can be used as building blocks to encrypt or decrypt messages of arbitrary length. There are numerous block ciphers available out there and some of them are broken or considered insecure by now. The probably most popular ciphers today are finalists of the AES competition. In 1997 the National Institute of Standards and Technology (NIST) decided to start a competition to choose a successor of the Data Encryption Standard (DES) [42]. This was necessary, because DES, which uses only a 56-bit key and a block size of 64 bits, became vulnerable to brute force attacks. Consequently the new algorithms were forced to support key sizes of 128, 192 and 256 bits and process a block size of 128 bits [48]. In 2000, NIST announced, that Rijndael was chosen out of the five finalists Rijndael [43], Serpent [4], Twofish [53], RC6 [51] and MARS [9], which were rated in that order. Rijndael, now known as the Advanced Encryption Standard (AES) [43], was especially chosen, because it offered a good combination of security and performance [49].

Despite there is only one winner, none of these algorithms is clearly broken or has some kind of known security vulnerability, rather they are still in use today. Because of their importance, it seems to be a good choice to speed up algorithms out of these five finalists. MARS will not be selected, because it is the last one of the five finalists and has not that much practical relevance in today's applications. RC6 is not royalty-free and therefore will not be selected either, last but not least because an integration into the kernel would be impossible. Furthermore it is pointless trying to speed up Rijndael (or AES) with SIMD instructions, because there exists a very fast and efficient hardware implementation, called AESNI [31], which is available with every processor, supporting AVX. With AESNI it is possible, to do one round of the encryption or decryption routine with a single instruction. A round in AES consists of four steps: a substitution step, a shift step, a mix step and one step, which combines the state with the round key. In practice a software implementation would replace most of this steps by some table lookups, but even with this technique we have no chance of being faster than one single instruction. After this considerations, there are two finalists left: Serpent and Twofish. Both still have practical relevance and as there exists no specific hardware implementation on generic processors, it is a good choice to accelerate this two algorithms.

#### 2.1.3 Serpent

Serpent [4] was the second best rated block cipher in the AES competition. As AES itself, it can be categorized as *substitution-permutation network* (SPN). A SPN is a series of mathematical operations, which consists of several rounds of substitutions and permutations. A substitution box, often referred to as S-box, is responsible for substituting a block of bits by another block of bits. As every operation in the SPN should be invertible to provide decryption, the S-box should output bits of the same length as the input and be injective and surjective. A permutation permutes all the bits, which the S-boxes give as output, and they can be used as input for the S-boxes of the next round. These two operations combined provide diffusion and confusion properties, which were already identified by Shannon in 1949 [54]. Diffusion means, that if the plaintext message changes slightly, the ciphertext should change completely. This is achieved by well chosen S-boxes. Confusion means, that changing the key slightly should change the ciphertext substantially.

$\hat{B}_0 := IP(P)$  $\hat{B}_{i+1} := R_i(\hat{B}_i)$  $C := FP(\hat{B}_{32})$

where

$R_i(X) = L(\hat{S}_i(X \oplus \hat{K}_i)) \qquad i = 0, \dots, 30$  $R_i(X) = \hat{S}_i(X \oplus \hat{K}_i) \oplus \hat{K}_{32} \qquad i = 31$

Figure 2.3: High-level pseudocode of Serpent

```

\begin{split} X_0, X_1, X_2, X_3 &:= \hat{S}_i(\hat{B}_i \oplus \hat{K}_i) \\ X_0 &:= X_0 <<<13 \\ X_2 &:= X_2 <<<3 \\ X_1 &:= X_1 \oplus X_0 \oplus X_2 \\ X_3 &:= X_3 \oplus X_2 \oplus (X_0 <<3) \\ X_1 &:= X_1 <<<1 \\ X_3 &:= X_3 <<<7 \\ X_0 &:= X_0 \oplus X_1 \oplus X_3 \\ X_2 &:= X_2 \oplus X_3 \oplus (X_1 <<7) \\ X_0 &:= X_0 <<<5 \\ X_2 &:= X_2 <<<22 \\ \hat{B}_{i+1} &:= X_0, X_1, X_2, X_3 \end{split}

```

Figure 2.4: Linear Transformation L

This is done by the permutations, because they exchange the bits in a way, that the different S-boxes again are able to provide diffusion by getting slightly different input. In every round, the round key, which is obtained in the key schedule, has to be adopted to the blocks in some way. This can be done by providing key-dependent S-boxes, but in Serpent the generated round keys are simply xor'ed with the intermediate state.

As all the AES competition candidates, Serpent has a block size of 128 bits and supports key sizes of 128, 192 and 256 bits. Serpent consists of 32 rounds, operating on four 32 bit doublewords (this corresponds to the block size of 128 bits). Compared to AES, which has ten, twelve or fourteen rounds, depending on the key size, Serpent is considered more secure, but AES is faster and therefore was selected as the winner. The authors of Serpent state that they were rather conservative on security issues and specified more rounds than actually necessary, just to be sure [4]:

16-round Serpent would be as secure as triple-DES, and twice as fast as DES. However, AES may persist for 25 years as a standard and a further 25 years in legacy systems, and will have to withstand advances in both engineering and cryptanalysis during that time. We therefore propose 32 rounds to put the algorithm's security beyond question.

Serpent encrypts 128 bit of plaintext P to 128 bit of ciphertext C in 32 rounds under the control of 33 128 bit subkeys  $\hat{K}_0, \ldots, \hat{K}_{32}$ . The cipher consists of an initial permutation IP, 32 rounds, each consisting of a key mixing operation, a pass through S-boxes and a linear transformation, and a final permutation FP. In the last round an additional key mixing operation is used, instead of the linear transformation. Figure 2.3 shows the high-level pseudocode of the encryption routine.  $\hat{B}_0, \ldots, \hat{B}_{32}$  are the intermediate values between the different rounds. Each round function  $R_i$  uses 32 copies of a single 4x4 S-box, which can be applied in parallel. For example in round  $R_0$ ,  $S_0$  is applied on bits 0, 1, 2 and 3 of  $\hat{B}_0 \oplus \hat{K}_0$  and returns the first four bits of an intermediate vector. After that  $S_0$  is applied on bits 4-7 of  $\hat{B}_0 \oplus \hat{K}_0$ , returning the next four bits of the intermediate vector and so on. The intermediate vector is then transformed by the linear transformation L, shown in figure 2.4, resulting in  $B_1$ . In figure 2.4 <<< donates left rotation by the given value, << donates left shift and  $\oplus$  is a simple xor operation. Round  $R_0$  is finished and the other rounds work exactly the same, as shown in the pseudocode. Serpent provides eight different 4x4 S-boxes, meaning that they map four input bits to exactly four output bits. Thus in figure 2.3,  $\hat{S}_i$  is the application of the S-box  $S_{i \mod 8}$  32 times on the subsequent 4 bit groups of the 128 bit input. The eight S-boxes  $S_0, \ldots, S_7$  are generated with a deterministic and iterative algorithm that is repeated until the S-boxes satisfy specific diffusion properties. The details of this algorithm and the properties the S-boxes satisfy after being generated can be looked up in the official publication [4]. For implementation issues the generation method is not relevant as all eight S-boxes are listed in the appendix of the publication. The initial and final permutations are listed in the appendix as well.

The concrete implementation of Serpent is usually done in bitslice mode. In this mode the initial and final permutation is not needed, because it was just constructed to make the bitslice implementation very simple.

|                                                  | #define S0(x0, x1, x2, x3, x4) ({ \                  |

|--------------------------------------------------|------------------------------------------------------|

|                                                  | x4 = x3; \                                           |

|                                                  | x3  = x0; x0 ^= x4; x4 ^= x2; \                      |

| unsigned char $s0[16] = {$                       | x4 = ~x4; x3 ^= x1; x1 &= x0; \                      |

| 3, 8, 15, 1,                                     | x1 ^= x4; x2 ^= x0; x0 ^= x3; \                      |

| 10, 6, 5, 11,                                    | x4  = x0; x0 ^= x2; x2 &= x1; \                      |

| 14, 13, 4, 2,                                    | x3 ^= x2; x1 = ~x1; x2 ^= x4; \                      |

| 7, 0, 9, 12                                      | x1 ^= x2;                                            |

| };                                               | })                                                   |

| Figure 2.5: Serpent S-box $S_0$ written as array | <b>Figure 2.6:</b> $S_0$ written as logical sequence |

ī

In fact the high-level pseudocode, shown in figure 2.3, still applies to this implementation, apart from the two permutations. The linear transformation L, shown in figure 2.4, was already presented in the form, it is needed for this implementation. The major difference between the explanation given above and the implementation presented here, is the multiple application of a S-box in the function  $\hat{S}_i$ . On a modern processor substituting 32 times 4 bit groups of 128 bit input data would be horrible slow, as the processor is at least capable of processing 32 bit doublewords. That is why the Serpent S-boxes were designed to be able to be applied in a more sophisticated way. The 128 bit input of  $\hat{S}_i$  is considered as four 32 bit doublewords. The S-box is then implemented as a sequence of logical operations (instead of 32 table lookups), which can be applied to these four words. With this logical sequence, the CPU implicitly processes the 32 table lookups in parallel. In figure 2.5 you see the Serpent S-box  $S_0$  written as classical array, like you would use it in conjunction with an ordinary table lookup. In figure 2.6 the corresponding logical sequence of  $S_0$ is shown. In this listing  $S_0$  is implemented as macro and gets the four 32 bit doublewords  $\times 0$  to  $\times 3$  as input and x4 is a temporary variable. Figure 2.6 was taken from the generic Serpent implementation in the Linux kernel, but both variants are available in the full submission package of the Serpent cipher for the AES competition as well. With these building blocks we have everything, we need to implement Serpent in an efficient way. The key mixing is just a xor of 128 bit and the linear transformation works with 32 bit doublewords as well as the substitution operation. All we have to do is to follow the pseudocode in figure 2.3 without the initial and final permutation, use the S-boxes as logical sequences, like in figure 2.6, and the linear transformation from figure 2.4. If we implement Serpent this way, like it is suggested in the official publication [4], we need no table lookups at all and the only memory operation in an encryption round is in fact the loading of the round key. Decryption has not been covered by now, but to keep things short it can be said that it works very similar, but everything has to be reversed. This is possible because the linear transformation and the eight S-boxes are invertible operations and of course the key mixing is invertible as well, because it is just a xor operation.

There is one more thing, we have not covered yet: The generation of the 33 128 bit subkeys  $\hat{K}_0, \ldots, \hat{K}_{32}$ , that are needed in every round and after the last round of en- or decryption, also referred to as key schedule. To generate the subkeys, we have to execute the following steps: First the user supplied key is padded to 256 bits and written as eight 32 bit doublewords  $w_{-8}, \ldots, w_{-1}$ . After that it is expanded to an intermediate key  $w_0, \ldots, w_{131}$  by the following affine recurrence:

$$w_i := (w_{i-8} \oplus w_{i-5} \oplus w_{i-3} \oplus w_{i-1} \oplus \phi \oplus i) <<<11$$

$\phi$  is the fractional part of the golden ratio  $\frac{1}{2}(\sqrt{5}+1)$  or  $0 \times 9 \in 3779b9$  in hexadecimal. Now the round keys are calculated from the intermediate keys using the eight S-boxes in bitslice mode again, i.e. implemented as logical sequences. Specific S-boxes are applied to four subsequent doublewords of the intermediate key, giving four doublewords of the real key or one 128 bit subkey for the corresponding round. We do not have to reimplement the key schedule, but just the encryption and decryption routines of Serpent, and therefore the detailed process of which S-boxes are applied in which order to parts of the intermediate key will be not explained here. If you already have generated the intermediate key, it is not very complicated, tough, and you might want to have a look at the official publication [4], if you are interested in the details of the key scheduling. Concluding this section, this has been a high-level description of Serpent with some additional informations on how an actual implementation could be done. In section 3.1 our own implementation will be explained in detail.

#### 2.1.4 Twofish

Twofish [53], as the third best rated block cipher in the AES competition, has the basic structure of a *Feistel network*. A Feistel network is a general method of transforming a function F into a permutation. One advantage of a Feistel network compared to a substitution-permutation network is that the function F does not need to be invertible, i.e. bijective. F takes n/2 bits of a block, consisting of n bits, and a round key as input and gives n/2 bits as output. The whole block of length n is divided into two parts of equal length and processed as follows: In each round the first half is the input of F and the output of F is xor'ed with the second half. After this, the two halves are swapped and processed in the next round exactly the same way. This can be repeated over a designated number of rounds. Two rounds of a Feistel network are called a *cycle*. With this technique we get an invertible cipher, possibly consisting of several rounds, even tough F is not necessarily invertible itself. Twofish is a 16-round Feistel network, i.e. takes 8 cycles, with a bijective function F. It is related to the former block cipher Blowfish [52], developed by Bruce Schneier, who amongst others also designed Twofish, as an alternative to DES. Both algorithms, Blowfish and Twofish, still play an important role in applications used today.

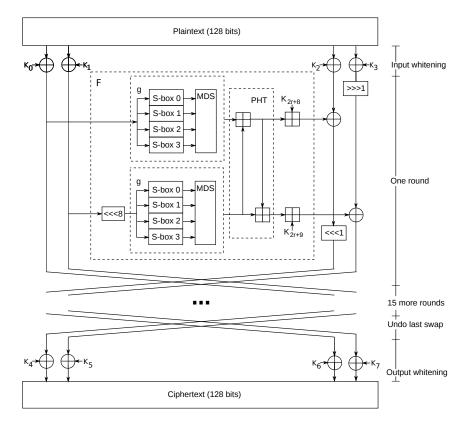

In contrast to Serpent, Twofish uses key-dependent S-boxes. To be more precise it uses four key-dependent 8x8 S-boxes. Additionally to the S-boxes there also exist round keys, which are xor'ed with the intermediate state in each round, and moreover Twofish uses so called *whitening keys*, which are xor'ed with the input block before the first round and with the output block after the last round. This key-whitening technique is used to hide the specific inputs to the first rounds' F function from an attacker and increases the difficulty of keysearch attacks. All these key-dependent components, the four S-boxes and 40 doublewords of subkey material (8 doublewords for key-whitening and 32 doublewords used as subkeys for the 16 rounds), are generated in the key schedule of Twofish. This makes the key schedule rather complex, but for the moment we assume, we have finished the key scheduling, generated all the key-dependent components and have a look at the encryption process. Of course Twofish has a block size of 128 bits and accepts key sizes of 128, 192 and 256 bits, because it is an AES candidate. Figure 2.7 gives a complete overview of the Twofish encryption algorithm. This illustration may look a bit complicated, but in fact it is a good visualisation of the whole process and you can see the Feistel structure of the algorithm. First of all let us explain the symbols: <<< and >>> donate left respective right rotations,  $\oplus$  stands for a xor operation of doublewords and  $\boxplus$  is the addition of two doublewords modulo  $2^{32}$ . The input block, 128 bits of plaintext, is first xor'ed with the first four doublewords of the whitening key. After that there follow 16 rounds, in which the first half of the block is processed by the function F and afterwards is xor'ed with the second half of the block. There is one difference between this structure and a pure Feistel structure: The two one bit rotations of the doublewords in the second half of the block, one after the xor'ing with the output of F and one before it. As rotations are invertible this is no problem and the advantage of a Feistel structure still applies. Apart from that everything works the usual way. The two halves are swapped and one round is finished. After the last round has been completed, the two halves are swapped again, to undo the last swap, and the ouput is xor'ed with the second four doublewords of the whitening key. The result of this operation becomes the 128 bits of ciphertext.

Now as the macrostructure has been shown, we need to take a closer look on the function F. F takes 64 bit data as input and processes it as two 32 bit doublewords. The first doubleword is directly processed by the function g and the second doubleword is left rotated by 8 bits, i.e. one byte, and after that processed by the function g as well. On the two doublewords, now named a and b, a *Pseudo-Hadamard-Transformation* (PHT) is applied. The PHT is a simple mixing operation and defined as:

$$a' = a + b \mod 2^{32}$$

$$b' = a + 2b \mod 2^{32}$$

As you can see in figure 2.7, this operation can be realized by just two additions of doublewords modulo  $2^{32}$ . Finally onto the two results of the PHT two doublewords, the subkey for this round, are added. Again this is done with an addition of doublewords modulo  $2^{32}$ . So in every round two 32 bit doublewords of subkey material are needed. Now it becomes clear, why there are 40 doublewords generated in the key schedule. In every round we need 2 doublewords, adding up to 32 doublewords in 16 rounds, and 8 doublewords are needed for the key-whitening process at the beginning and end of the encryption routine. With the addition

Figure 2.7: Overview of the Twofish encryption algorithm

of the round key the function F is finished.

The last component in the encryption routine, which has to be explained, is the function g. However it is the most complicated component. g takes one 32 bit doubleword as input and outputs one 32 bit doubleword. The doubleword is split into four bytes and every byte is processed by one of the four key-dependent 8x8 S-boxes. The four results are interpreted as a vector of length 4 over GF(2<sup>8</sup>), which is multiplied by the 4x4 MDS matrix giving the result of g. MDS stands for *maximum distance separable* and a MDS matrix is a matrix operating over a finite field with certain diffusion properties. These diffusion properties are helpful, to ensure that small changes in the plaintext lead to huge changes in the ciphertext. This connection has already been pointed out in section 2.1.3 about Serpent. The MDS operation looks like this:

$$\begin{pmatrix} z_0 \\ z_1 \\ z_2 \\ z_3 \end{pmatrix} = \begin{pmatrix} 01 & \text{EF} & 5\text{B} & 5\text{B} \\ 5\text{B} & \text{EF} & \text{EF} & 01 \\ \text{EF} & 5\text{B} & 01 & \text{EF} \\ \text{EF} & 01 & \text{EF} & 5\text{B} \end{pmatrix} \cdot \begin{pmatrix} y_0 \\ y_1 \\ y_2 \\ y_3 \end{pmatrix}$$

(2.1)

The matrix you see is the Twofish specific MDS matrix from the official publication [53]. The values  $y_0, \ldots, y_3$  are the four results of the application of the S-boxes 0 to 3 and  $z_0, \ldots, z_3$ , as result of the MDS operation, lead to the result of the function g by being interpreted as one doubleword again. In fact the operation (2.1) is an usual matrix-vector multiplication, but the computations are done in the field GF(2<sup>8</sup>).

$GF(2^8)$  is the - except from isomorphisms - unambiguous finite field with 256 elements and can be represented as GF(2)[x]/v(x), where v(x) is an irreducible polynomial of degree 8 over GF(2). Maybe you know GF(2) better as  $\mathbb{Z}/2\mathbb{Z} = \mathbb{Z}_2$ , which is the finite field with only two elements. In this field addition is the usual addition from  $\mathbb{Z}$  modulo 2, which is in fact just the xor operation, and multiplication is trivial as there only exist the elements 0 and 1. Every element of  $GF(2^8)$  now can be represented as polynomial with at most degree 7 and coefficients out of GF(2), because  $GF(2^8) = GF(2)[x]/v(x)$ . Addition in  $GF(2^8)$  is consequently equivalent to the addition of two polynomials with coefficients out of GF(2), that is to say

the coefficients just have to be xor'ed. Addition in  $GF(2^8)$  is an efficient operation, but multiplication is non-trivial. You have to do the multiplication, like you would multiply two ordinary polynomials, but every operation is done modulo v(x). This means that if you multiply, and any term with degree 8 or higher occurs, you have to remove this term by adding the terms of degree 7 or lower taken from v(x) to the result. This works because v(x) equals 0 in  $GF(2^8)$  and subtraction is the same operation as addition in GF(2). Elements of  $GF(2^8)$  are typically represented as exactly one byte, containing the coefficients for the corresponding polynomial of at most degree 7. This makes addition even easier, because you just have to xor two bytes, to realize an addition in  $GF(2^8)$ .

After this short excursion to finite field arithmetic, let us come back to our MDS operation. The irreducible polynomial chosen for Twofish is  $v(x) = x^8 + x^6 + x^5 + x^3 + 1$ . All the elements listed in the matrix in (2.1) are elements of  $GF(2^8) = GF(2)[x]/v(x)$  with this specific v(x). The first component  $z_0$  of the result vector is calculated like this:

$$z_0 = (01 \odot y_0) \oplus (\text{EF} \odot y_1) \oplus (5\text{B} \odot y_2) \oplus (5\text{B} \odot y_3)$$

(2.2)

This entire calculation is done in  $GF(2^8)$ , at which  $\oplus$  stands for addition (a simple byte xor) and  $\odot$  for the complex multiplication in  $GF(2^8)$ . The other components  $z_1, z_2, z_3$  are calculated exactly the same way. With this operation the function g is finished and the entire encryption process has been described. The decryption routine has not been covered, but since Twofish has Feistel structure, it is not necessary to provide reversed S-boxes or even a reversed function F for the cipher. All we have to do is to apply the key-whitening in the reversed order and use the same structure as in figure 2.7. F depends on the round keys and so the 16 applications of F have to be applied in reverse order, too. The function F itself, however, does not change in this entire process. The one non-Feistel element in this cipher, the two one bit rotations, have to be reversed as well, because they are not part of the function F. This means, that if the encryption has been implemented, very few changes have to be made to implement the decryption routine. The last question is how to get the 40 doublewords  $K_0, \ldots, K_{39}$  of key material for the encryption and decryption routine. Twofish has a really complex key schedule, which generates the 40 doublewords (8 doublewords whitening keys and 32 doublewords as round keys) and the four key-dependent 8x8 S-boxes from the user supplied key. It would probably take several pages to describe the key schedule in detail and as we do not need to implement it, we will not cover it here. If you are interested in the details, you should take a look at the Twofish Paper [53]. In all cases the user supplied key is padded to full 256 bits and the number of rounds is independent of the size of the supplied key.

There is one major optimization, which can be made, when implementing Twofish. Implementing the encryption routine the way it was introduced here, would result in a bottleneck, because of the function g. As already mentioned the MDS operation is a complex and expensive operation, but if you have a close look at figure 2.7, you will see that the MDS operation is applied to the four bytes after the processing with the four S-boxes. Moreover the MDS operation is just a matrix multiplication and therefore a linear operation over  $GF(2^8)$ . This means, it is possible to combine the application of the S-boxes and the MDS operation, thus the entire function q, to four table lookups and three xor operations. However this technique needs more space, because instead of four 8x8 S-boxes, i.e. 1024 bytes, four 8x32 tables, i.e. 4096 bytes, are needed. This trick works by precalculating the MDS operation for every byte of the four S-boxes. Every byte of the first S-box is multiplied over  $GF(2^8)$  with every element of the first column of the MDS matrix. The resulting 4 bytes are saved as 32 bit doubleword in a new 8x32 lookup table at the same position from where the byte was taken out of the first S-box. The same procedure is carried out with the second S-box and the second column of the MDS matrix, and so on. After the precalculating, we now have four 8x32 lookup tables, which we can store instead of the four key-dependent S-boxes. The S-boxes are no longer needed and may be discarded. So instead of implementing q like described before, we now take the four input bytes and do four table lookups into our precalculated tables. The four resulting doublewords are xor'ed and this is the result of the function q. If you have a look at the calculation (2.2), where the first result byte was calculated the ordinary way, you will see the three xor operations and the four multiplications, which now can be replaced by our table lookups, because the lowest byte of the doubleword in a specific table corresponds to a specific term in (2.2).

There is one more small modification, which can be made. The 8 bit left rotation before one of the two applications of g can be saved, if we provide two functions  $g_1$  and  $g_2$ , which differ in the order in which

byte of their input they use for which lookup table. This will increase code size slightly, but we save at least one instruction in every round. With this two tricks, we have significantly simplified the encryption routine, because we do not need multiplications over a finite field anymore. The only operations that are needed to implement the encryption routine are xor, rotations, additions and table lookups. In section 3.2 we will use exactly this optimizations to implement the Twofish encryption and decryption routine as fast as possible.

#### 2.1.5 Blowfish

After having a look at the AES finalist Twofish, it is consequential to have a look at the predecessor Blowfish [52], too. Blowfish is not an AES candidate, but nevertheless it is still widely used in today's applications. Blowfish has the structure of a pure Feistel network and iterates an encryption round function 16 times. There are no exceptions, like the two one bit rotations in the Twofish encryption process. The block size of Blowfish is just 64 bits and the key size can vary between 32 and 448 bits. There are always 16 rounds, independent of the chosen key size. In the encryption routine Blowfish uses 18 32 bit subkeys and four key-dependent 8x32 S-boxes. The 18 doublewords of subkey material and the key-dependent S-boxes are generated during the key scheduling process of Blowfish. The details of the key scheduling algorithm will not be covered here, because we do not need to reimplement this part. Basically it works this way: The encryption routine itself is used to generate the subkey material and the S-boxes. First of all the 18 doublewords and the S-boxes are initialized with the hexadecimal digits of  $\pi$ . After that the subkeys are xor'ed with the user supplied key and an all-zero block is encrypted. The result of this encryption process replaces the first two doublewords of subkey material. The encryption routine now gets the result as input to replace the next two doublewords. This process is repeated until all values of the subkey material and the S-boxes have been replaced. In total there are 521 iterations required to finish the key schedule, making this a rather expensive operation.

By now we assume, that the key schedule has been finished successfully and the 18 doublewords of subkey material and the four key-dependent 8x32 S-boxes are available. The encryption routine gets a 64 bit block as input and outputs a 64 bit block. First of all the input block is divided into two 32 bit doublewords. Now there follow sixteen rounds, that operate on the two doublewords. In every round the left doubleword is xor'ed with the corresponding subkey doubleword and afterwards processed by the function F. The result of F is xor'ed with the right doubleword and then the two doublewords are swapped. With this operation one round is finished and the next one follows. After the sixteen rounds are finished, the left and the right doubleword are swapped again, to undo the swap of the last round, the right doubleword is xor'ed with the 17th subkey doubleword and the left doubleword results in the output block of the blowfish encryption routine.

As you can see, the encryption routine of Blowfish is really simple to describe and by far simpler than the one for Twofish. Moreover the Feistel structure of the algorithm is clearly visible. The last thing we have to explain is the function F. F gets a doubleword as input and divides it into four bytes. For every byte a lookup into one of the four key-dependent 8x32 S-boxes is made in order, resulting in four doublewords. Now the first two doublewords are added modulo  $2^{32}$  and the result is xor'ed with the third doubleword. The result of this operation is added to the fourth doubleword modulo  $2^{32}$  leading to the result of F.

Now all components of the Blowfish encryption routine have been described. Basically one round in this routine consists of a xor operation with the round key and four table lookups followed by two additions and one xor operation. Although the key schedule is rather complex, the encryption routine is very simple, at least if the hardware supports operations on 32 bit doublewords. There are 4168 bytes required to store the Blowfish context among subsequent encryption calls. The decryption routine works equivalent to the encryption routine, because of the Feistel structure, and just the subkeys have to be supplied in reverse order.

#### 2.1.6 Cast-128

Cast-128 [1], which is also called Cast5, is another block cipher, which is similar to Blowfish. It is still the default cipher in GPG according to the manpage. Cast-128 is available worldwide on a royalty-free basis and therefore it is also available in the Linux kernel. As Blowfish, Cast-128 is a Feistel network with 64 bit block size. The key may have sizes between 40 and 128 bits. Cast-128 consists of 12 or 16 rounds, depending on the size of the key. For key sizes shorter than or equal to 80 bits only 12 rounds are used and for key sizes longer than 80 bits the 16 round version is used. The two versions do not differ in anything else, but the number of the rounds and therefore we will focus on the 16 round version in this explanation. In the encryption routine Cast-128 makes use of 16 doublewords of subkey material, called masking keys, and 16 bytes of rotation values. The latter ones are used for key-dependent rotations, a new feature, which has not occurred in the ciphers that have been described by now. Furthermore four 8x32 S-boxes are needed in the encryption routine, but they are not key-dependent, but fixed, regardless of the user supplied key. The 16 masking keys and the 16 rotation values are generated during the key scheduling algorithm of Cast-128, which will not be described here. However the key scheduling is not very complicated. It uses another four S-boxes in addition to the four S-boxes needed in the encryption routine the publication [1].

The encryption routine processes a 64 bit block. The block is divided into two 32 bit doublewords and then sixteen respectively twelve rounds are performed. In each round the right doubleword is processed by a round specific function and the result is xor'ed with the left doubleword. After that the two doublewords are swapped and the next round begins. When all rounds are finished the two doublewords are swapped again, to undo the swap of the last round, and the combination of the two doublewords is the resulting 64 bit output block of the encryption routine. This represents the structure of a typical Feistel network.

$$\begin{split} f_1(D,i): & I_0, I_1, I_2, I_3 = ((Km_i \boxplus D) <<< Kr_i) \\ & f_1(D,i) = ((S_1(I_0) \oplus S_2(I_1)) \boxminus S_3(I_2)) \boxplus S_4(I_3) \\ f_2(D,i): & I_0, I_1, I_2, I_3 = ((Km_i \oplus D) <<< Kr_i) \\ & f_2(D,i) = ((S_1(I_0) \boxminus S_2(I_1)) \boxplus S_3(I_2)) \oplus S_4(I_3) \\ f_3(D,i): & I_0, I_1, I_2, I_3 = ((Km_i \boxminus D) <<< Kr_i) \\ & f_3(D,i) = ((S_1(I_0) \boxplus S_2(I_1)) \oplus S_3(I_2)) \boxminus S_4(I_3) \end{split}$$

Figure 2.8: Round-dependent functions of CAST-128

The round specific functions are listed in figure 2.8. There are three different functions, which differ just in the operations carried out on the doublewords, but the basic structure of all three functions is the same. In this figure  $\oplus$  denotes xor,  $\boxplus$  denotes addition modulo  $2^{32}$ ,  $\square$  stands for a subtraction modulo  $2^{32}$  and <<< denotes logical left rotation by the given number of bits. The functions are used in the order listed in this figure, meaning that in the first round the function  $f_1$  is used, in the second round  $f_2$  and in the third round  $f_3$ . After that, the function  $f_1$  is used again in the fourth round and so on. All functions get the right doubleword D from the current encryption round as input and use the current round number i. First a specific operation with the corresponding masking key  $Km_i$  of the round is carried out and afterwards the result is left rotated by the rotation value  $Kr_i$  of that round. The result of this rotation is interpreted as four bytes, where  $I_0$  is the most significant byte and  $I_3$  is the least significant byte. For each byte a lookup into the fixed 8x32 S-boxes  $S_1, \ldots, S_4$  is performed and the results of this lookups are combined according to the operations listed in figure 2.8.

With the round specific functions the whole encryption routine has been explained and we do not need to explain the decryption routine in detail, because of the Feistel structure. Of course the masking keys and the key-dependent rotation values have to be applied in reverse order, as well as the functions  $f_1$ ,  $f_2$  and  $f_3$ , but the rest of the decryption routine works exactly like the encryption part. To summarize things, the Cast-128 cipher uses basic operations on doublewords and table lookups. The rotations with key-dependent rotation values are not basic operations, but we will show in section 3.4, how we can implement them with SIMD instructions.

#### 2.1.7 Cast-256

From Cast-128 it is no big step to the successor Cast-256 [2], also called Cast6, and therefore this will be the last cipher, which will be covered in this thesis. Cast-256 has been submitted to the AES Competition, but was not among the five finalists mentioned above. Consequently it has a block size of 128 bits and accepts key sizes of 128, 160, 192, 224 and 256 bits. The key sizes 128, 192 and 256 bits are necessary for an AES candidate. Cast-256 works with 48 rounds, also referred to as twelve quad-rounds, and the number of rounds is independent of the key size. The four fixed 8x32 S-boxes and the three functions  $f_1$ ,  $f_2$  and  $f_3$  are reused from the Cast-128 algorithm. The encryption routine of Cast-256 uses 48 masking keys and 48 rotation values, which have the same meaning, as they had with Cast-128. They are generated in the Cast-256 key schedule, which will not be described here.

Figure 2.9: Q and  $\overline{Q}$  of CAST-256

Let us assume the 48 doublewords of masking keys and the 48 bytes of rotation values have been properly generated. The encryption routine now executes six forward quad-rounds Q and afterwards six reverse quad-rounds  $\overline{Q}$ , which both are shown in figure 2.9. The input of the first quad-round is the input of the encryption routine and after that, the output of the previous quad-round is taken as input for the next quadround. In the end the output of the last reverse quad-round results in the output of the encryption routine. The reverse quad-round  $\overline{Q}$  is, as the name suggests, the reverse operation of the quad-round Q. As you can see in figure 2.9 the operations are just listed in the reverse order and therefore it is sufficient to explain just the quad-round Q in detail. Q gets 128 bits of data as input and interprets them as four doublewords A, B, C and D. Now the functions  $f_1$ ,  $f_2$  and  $f_3$  from the Cast-128 algorithm are called with the arguments shown in figure 2.9. The round argument goes from 0 to 47 and that is why all the 48 masking keys and rotation values are used by the subsequent invocations of the different functions. The whole encryption routine is described by the two quad-rounds Q and  $\overline{Q}$ , because both variants are just called six times. The decryption routine calls the six quad-rounds and the six reverse quad-rounds in the same order as the encryption routine, but supplies the quad-round numbers in the reverse order. So instead of supplying the values 0 to 11 the values 11 to 0 are supplied. This works, because the instructions in both variants are listed in the reverse order to each other. As you might have noticed many parts of the Cast-128 cipher can be reused in the Cast-256 implementation.

### 2.2 Advanced Vector Extensions

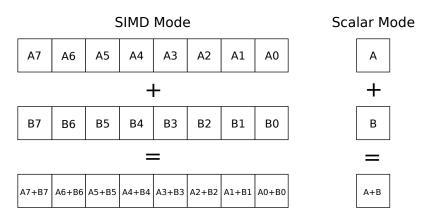

Intel's *Advanced Vector Extensions* (AVX) are a set of instructions for *Single Instruction Multiple Data* (SIMD) operations. A SIMD operation is a simple operation, like addition, multiplication or a boolean operation, which is applied on multiple, equal sized and packed data in parallel. Only one instruction is needed to process the data, whereas without SIMD multiple instructions would be used. Consequently instructions can be saved by this technique, provided that an algorithm is suitable for being parallelized this way. Figure 2.10 shows an illustration of how SIMD operations work compared to scalar operations.

AVX was developed for the continued need of vector performance in scientific applications, visual processing, recognition, gaming, physics, cryptography and other areas of applications [34]. Especially the vector performance in the field of cryptography is interesting for this thesis. The first processors supporting AVX were the Intel Sandy Bridge processors shipped in Q1, 2011 [36]. AMD provides AVX support with the Bulldozer processors shipped in Q3, 2011. At first AMD was working on its own SIMD instruction set,

Figure 2.10: SIMD vs. scalar operations [36]

called SSE5, but in May 2009 they decided to replace SSE5 with three new extensions XOP, CVT16 and FMA4 and to stay compatible with Intel's AVX [26]. The GNU Compiler Collection (GCC) supports AVX at least since version 4.6 [27] and the Linux Kernel since version 2.6.30 [55]. Explicit operating system support is required, because the registers used by AVX have to be properly saved and restored across context switches.

The new instructions extend the previous SIMD instructions by adding some interesting new features. The registers have been expanded to 256 bits and a nondestructive, three-operand syntax has been added. The details will be discussed in the following sections. To detect the availability and support of AVX on the hardware, it is possible to use the cpuid instruction. If AVX is supported by the hardware, the Bits 27 and 28 in the %ecx register are set after executing the instruction. The operating system support has to be checked as well. Therefore the xgetby instruction is needed and the Bits 1 and 2 (XMM and YMM state support) in the feature-enabled mask must be set. The whole process is shown in figure 2.11.

```

avx_supported:

mov $1, %eax

cpuid

and $0x018000000, %ecx

cmp $0x018000000, %ecx ; check OSXSAVE, AVX feature flag

jne .Lnot_supported

; specify 0 for XFEATURE_ENABLED_MASK register

xor %ecx, %ecx

xgetby

: result in %edx:%eax

and $0x06, %eax

cmp $0x06, %eax

; check OS has enabled XMM and YMM state support

jne .Lnot_supported

mov $1, %eax

; return value true

jmp .Ldone

.Lnot_supported:

xor %eax, %eax

; return value false

.Ldone:

ret

```

Figure 2.11: Checking for AVX support on hardware and operating system [34]

#### 2.2.1 Registers

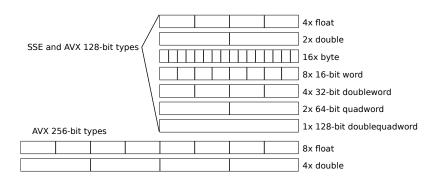

AVX introduces support for 256 bit wide SIMD registers. The 8 registers YMM0 to YMM7 are available in operating modes, that are 32 bit or less and in 64 bit mode the 16 registers YMM0 to YMM15 can be used. As AVX is an extension to the previous SIMD offerings, like the Streaming SIMD Extensions (SSE), the lower 128 bits of the YMM registers correspond to the respective 128 bit XMM registers, already known from SSE. This makes it possible to use AVX and SSE instructions together in the same application, tough it is not recommended, because AVX to SSE transitions have an impact on performance. In cases where

Figure 2.12: AVX and SSE data types [36]

the source code can be modified, this is not a problem, because for every SSE/SSE2 instruction there exists a new corresponding or equivalent AVX instruction. However, there might be cases, in which the code cannot be modified, for example if closed source third party libraries have to be used. In this case, mixing AVX instructions with legacy SSE instructions is not avoidable and a so called *transition penalty* is caused. The impact on performance can be minimized by using the vzeroupper instruction after the last AVX and before the first SSE instruction. This instruction clears the 128 upper bits of all YMM registers, which cannot be used by the legacy SSE instructions. The Intel Software Development Emulator [10] supports checking for transition penalties and shows, where vzeroupper instructions have to be inserted. AVX instructions, which operate on a specific XMM register, which corresponds to the lower 128 bits of the respective YMM register, always set the upper 128 bits of that YMM register to zero. This means, it is not possible to operate on just the lower part of a register using XMM operands and keep data stored in the upper part at the same time.